# High Performance Low Power Hall-Effect Sensor

# MHA100KN

### **FEATURES**

- Low power CMOS process

- Wide operation voltage range: 1.65~5.5V

- Ultra-low power consumption, <5uA@1.8V

- Good RF noise immunity

- Omnipolar operation

- Dual output, Unipolar Hall switch for N and S

- -40°C to +85°C operation

- RoHS compliant

- DFN4 package with 1.0mmx1.4mmx0.37mm

## **APPLICATIONS**

- TWS headset

- Smart meter

- Cover switch

## **DESCRIPTION**

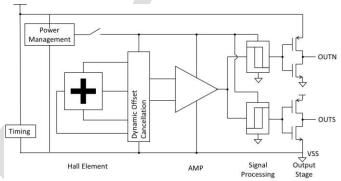

Figure 1: Signal Path

**SPECIFICATIONS** (Measurements @ 25 °C, unless otherwise noted; V<sub>DD</sub>=1.8V unless otherwise specified)

| Parameter                                   | Conditions               | Min                  | Тур                  | Max                  | Units |

|---------------------------------------------|--------------------------|----------------------|----------------------|----------------------|-------|

| Supply Voltage (V <sub>DD</sub> )           |                          | 1.65                 | 1.8                  | 5.5                  | V     |

| Supply Current                              |                          |                      | 2.5                  | 5.0                  | μA    |

|                                             | -40~85 °C                |                      | 2.5                  | 10.0                 | μA    |

| Power Down Current                          |                          |                      | 1.0                  |                      | nA    |

| Operating Temperature                       |                          | -40                  |                      | 85                   | °C    |

| Storage Temperature                         |                          | -55                  |                      | 125                  | °C    |

| Awake Tim (T <sub>awake</sub> )             |                          |                      | 50                   | 100                  | μs    |

| Period (T <sub>period</sub> )               |                          |                      | 50                   | 100                  | ms    |

| Duty Cycle                                  |                          |                      | 0.05                 |                      | %     |

| Output High (V <sub>OH</sub> )              | I <sub>OUT</sub> =+0.5mA | V <sub>DD</sub> -0.3 | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 | V     |

| Output Low (VoL)                            | I <sub>OUT</sub> =-0.5mA | -0.3                 | 0.1                  | 0.3                  | V     |

| Output Current                              |                          | -0.5                 |                      | 0.5                  | mA    |

| Magnetic Opening Point (BoP)                |                          | 27                   | 37                   | 47                   | Gauss |

| Magnetic Releasing Point (B <sub>RP</sub> ) |                          | 20                   | 30                   | 40                   | Gauss |

| Hysteresis Window (B <sub>HYS</sub> )       |                          | 2                    | 7                    |                      | Gauss |

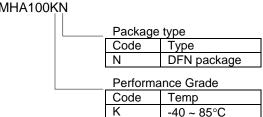

# ORDERING GUIDE MHA100KN

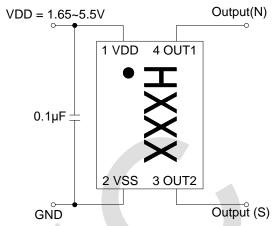

#### **PIN DESCRIPTION**

| Pin NO. | Pin Name | Description             |

|---------|----------|-------------------------|

| 1       | VDD      | Power supplier          |

| 2       | VSS      | Connected to Ground     |

| 3       | OUT2     | S pole detection output |

| 4       | OUT1     | N pole detection output |

**Caution:** Electro Static Discharge (ESD) sensitive device.

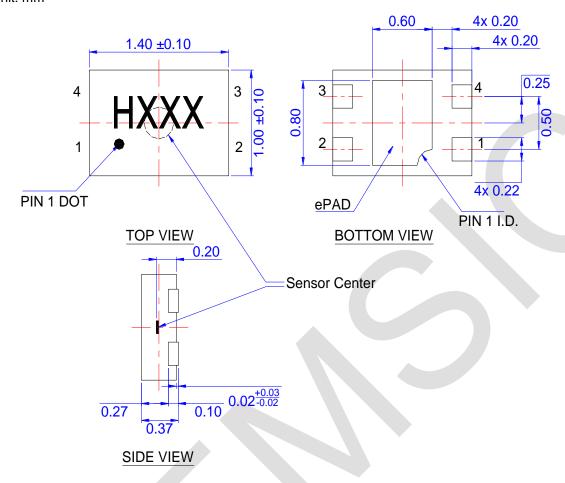

#### **PACKAGE ILLUSTRATION**

DFN4 package with 1.0mmx1.4mmx0.37mm size.

Figure 2: Package illustration

#### HARDWARE DESIGN CONSIDERATION

It is necessary to keep VDD voltage clean for best noise performance. A low-ESR bypass cap is required and recommended value is  $0.1\mu F.$  It should be placed close to the device as much as possible.

Figure 3: Connection diagram

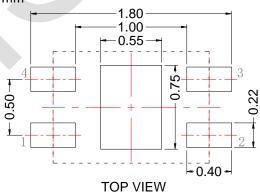

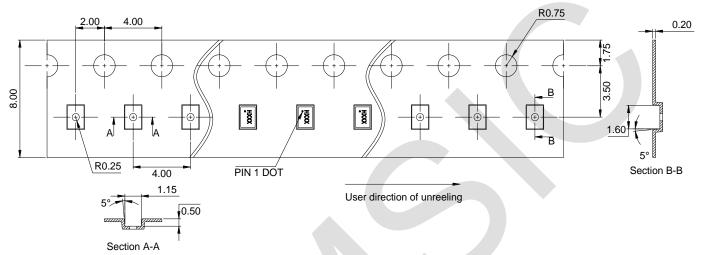

#### **LAND PATTERN**

- 1. The device routing should be symmetric.

- 2. Recommended land pattern of PCB is shown in Figure 3.

- 3. Thickness of stencil should be 0.1mm.

Unit: mm

Figure 4: Recommended land pattern

#### THEORY OF OPERATION

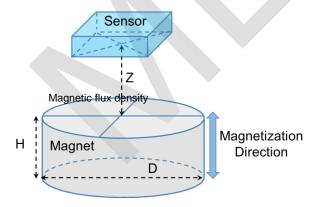

This Hall switch is fully integrated CMOS IC. It output high-low signal following magnetic field changing. Normally it works with a magnet and detect the magnet close and away.

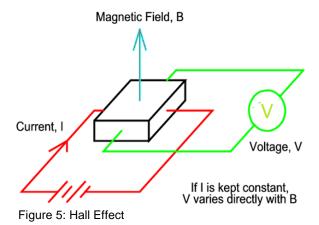

#### The Hall Effect

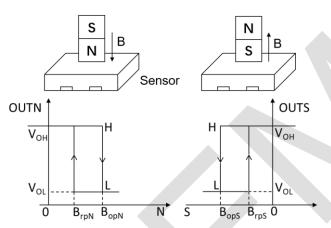

Figure 6: Output signals of OUTN and OUTS pins

Figure 7: Sensor and magnet

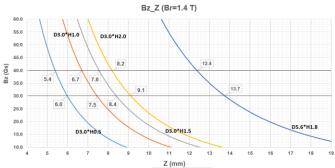

Figure 8: Field by magnet (different size and distance)

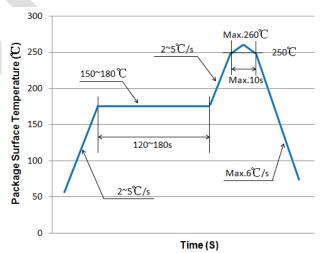

#### **SOLDER REFLOW PROFILE**

- Reflow is limited by 2 times. Second reflow should be applied after device has cooled down to room temperature (25°C).

- Recommended reflow profile for Pb free process is shown in Figure 3. The time duration of peak temperature (260°C) should be limited to 10 seconds.

- 3. Type 4 solder paste is recommended for a better SMT quality.

Figure 9: Recommended solder reflow profile

#### **MANUAL SOLDERING**

- 1. Soldering/repairing MHA100 manually via solder iron or heater gun is not recommended.

- 2. Avoid bending or torqueing the PCB after the sensor is assembled.

#### **PACKAGE OUTLINE DIMENSION**

Unit: mm

Figure 10: Mechanical package outline dimensions

#### Notes:

- a) Sensitive area located at the center of package within 0.3mm diameter circle.b) ePAD can be tied to the VSS or Floating.

- c) Unless otherwise specified, Tolerances is ±0.05mm.

#### **TAPE AND REEL PACKING**

Products are put into carrier tape according to marking direction. The quantity for each full reel is 4000pcs per reel with 7" lock reel. Please refer to Figure 6

Details for tape and reel packing as below:

- a) MHA100 tape and reel carriers are in accordance with ANSI/EIA-481

- b) Product pin 1 orientation: Upper Left

- c) Tape and reels are NOT designed to be baked at high temperatures

- d) Each tape and reel is typically dry packed in a moisture barrier bag (MSL1).

Figure 11: Carrier tape dimension and device orientation